Parallel Input Serial Output Shift Register Vhdl Code

Parallel Out Shift Register using D-Flip Flop (VHDL Code). Parallel OUT Shift Register using. Design of Serial IN - Serial Out Shift Register u. N bit shift register (Serial in Serial out) in VHDL. --serial input s_out: out std_logic --serial output ). Shift register parallel in serial out.

Parallel Input Serial Output Shift Register Vhdl Code

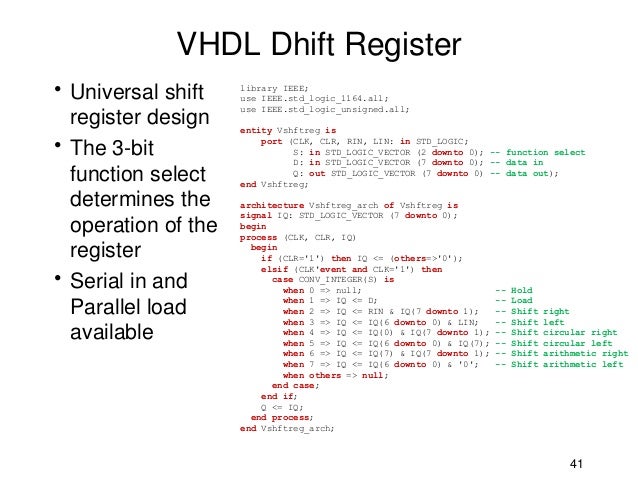

Library IEEE; use IEEE.STD_LOGIC_1164. ALL; use IEEE.STD_LOGIC_ARIT H.ALL; use IEEE.STD_LOGIC_UNSIGNED.A LL; entity siso is Port ( sin,clk,rst: in STD_LOGIC; q: inout std_logic_vector(2 downto 0); sout: out STD_LOGIC); end siso; architecture Behavioral of siso is COMPONENT DFF PORT (data,clock,rst:in std_logic;output:out std_logic); end component; begin d0: dff port map(sin,clk,rst,q(0)); d1: dff port map(q(0),clk,rst,q(1)); d2: dff port map(q(1),clk,rst,q(2)); d3: dff port map(q(2),clk,rst,sout); end Behavioral.